74HC595简介

74HC595是一个8位串行输入、并行输出的位移缓存器:并行输出为三态输出。在SCK 的上升沿,串行数据由SDL输入到内部的8位位移缓存器,并由Q7'输出,而并行输出则是在LCK的上升沿将在8位位移缓存器的数据存入到8位并行输出缓存器。当串行数据输入端OE的控制信号为低使能时,并行输出端的输出值等于并行输出缓存器所存储的值。

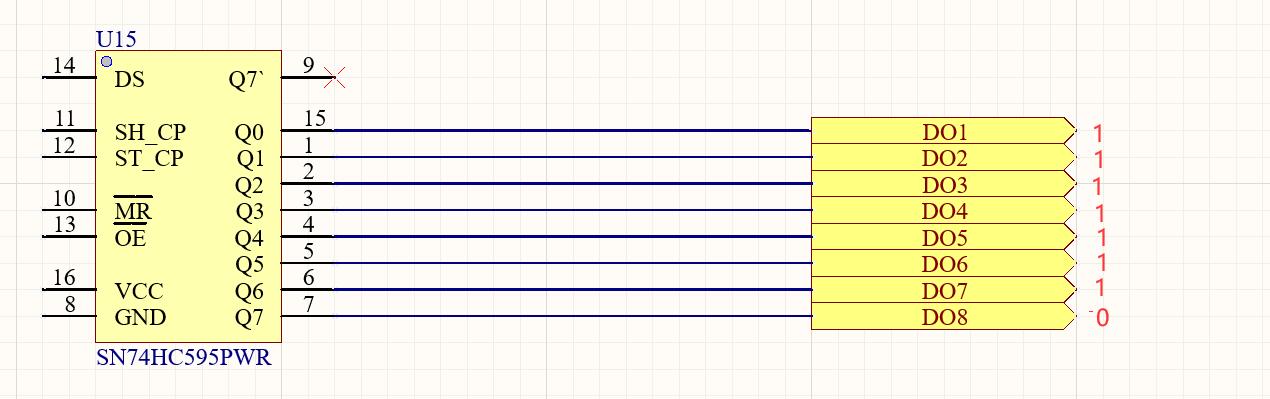

简单点就是串行输入并行输出,因为在不级联的情况下只有8个输出IO口所以一般串行数据输入为8位。74HC595原理图

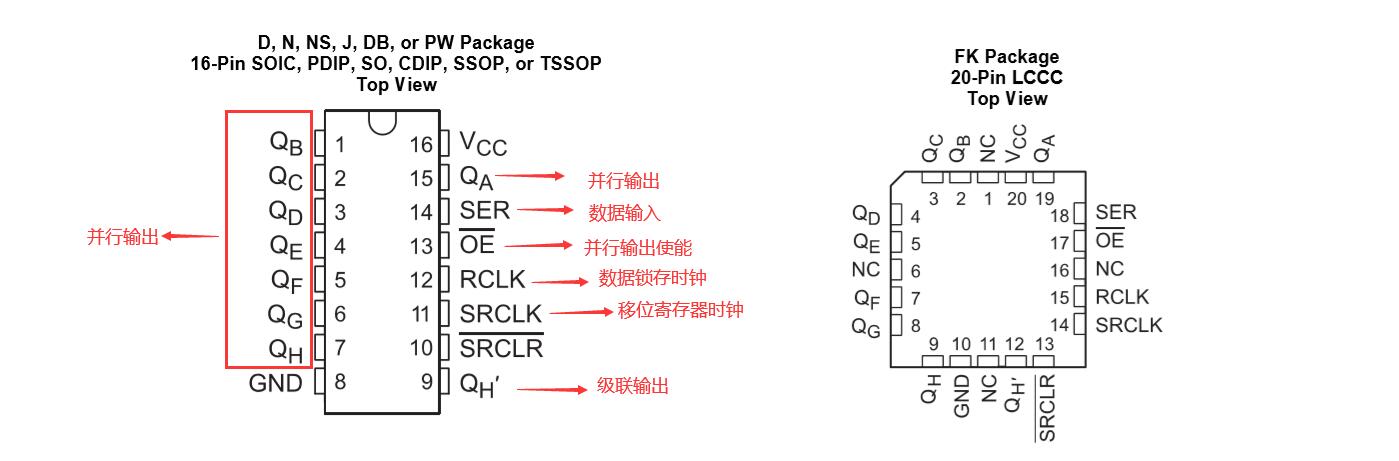

74HC595引脚介绍

并行输出引脚QA–QH(Q0-Q7)

在74HC595器件中一般对应的PIN脚是pin15,pin1,pin2,pin3,pin4,pin5,pin6,pin7,pin8.作用是将写入74HC595的8位串行数据并行输出(数字信号),从移位寄存器输入的第一个数据从pin8输出,以此类推。数据输入引脚 SER(DS)

74HC696可能不同厂商和型号的不同对于数据输入引脚的名称可能不同SER或者DS均为相同功能 一般位于74HC595器件的pin14脚位,数据的传输是根据该pin的高低电平和时钟信号(移位寄存器时钟)配合使用移位寄存器时钟 SH_CP(SRCLK)

该IO为移位寄存器提供时钟一般器件在器件的pin11,上升沿(不等于高电平)的时候读取数据,举例 当SH_CP(SRCLK)为上升沿时数据输入引脚SER(DS)为高电平则数据为1,如果在上升沿为低电平则为0.锁存器时钟 ST_CP(RCLK)

pin12为74HC595锁存器的时钟信号,与移位寄存器时钟相同,都是上升沿有效,当pin11上升沿时,将移位寄存器中的数据锁存到锁存器中,除非使用复位,数据只有在下次锁存时才会被替换(丢失)输出使能 OE 低电平有效

OE是74HC595的并行输出使能管脚pin13,当OE被拉低时数据从锁存器寄存器输出到并行IO上主复位MR

pin10,MR是主复位 ,低电平有效,低电平时,清空移位寄存器中已有的bit数据,一般不用,接高电平即可。级联输出 Q7(QH)

pin9,一般在级联上会用到,当上一级数据超过8位时,数据会向下一级移动,这个过程是自动的,例如当串行数据输入脚输入16位数据0xaabb,如果我们按照顺序发送0xaa,0xbb.当开始发送0xbb的时候,前面发送的0xaa就会自动输出到下一级的串行输入io上。数据发送过程简单描述图

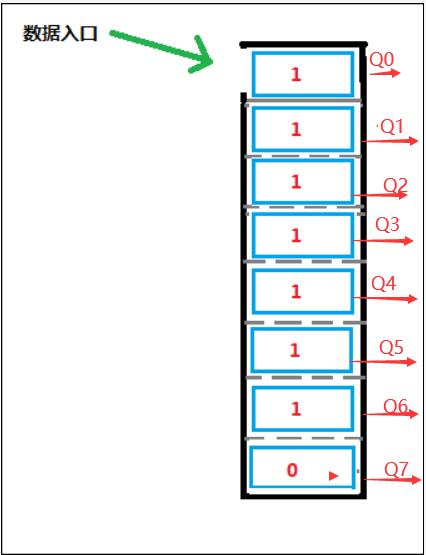

发送数据0111 1111 先发送高位

对照输出

驱动程序

按照先发送高位再低位的顺序,目前增加两个级联,IO的定义没有在里面,单片机不同,自己做定义

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

//简单延时函数

void Delay(int i)

{

while(i)

{

i--;

}

}

//74HC595发送函数 8位 先高位发送

void HC595_Write_8(uint8_t DATA)

{

for(int i=0;i<8;i++){

if ((DATA&0x80)==0x80)

{

DS_ON(); //数据发送1

}

else

{

DS_OFF(); //发送0,对应拉低pin脚

}

//上升沿发送数据

SH_CP_ON(); //创造上升沿拉高 移位寄存器时钟pin脚

DATA<<=1; //右移一位

SH_CP_OFF(); //拉低

}

}

//74HC595发送函数 16位 高字节先发送

void HC595_Write_16(uint16_t DATA)

{

HC595_Write_8(DATA>>8);

HC595_Write_8(DATA);

}

//74HC595数据输出函数 16位

//因为是两个HC595级联 所以需要16位数据 同时输出

void HC595_OUT_16(uint16_t DATA)

{

HC595_Write_16(DATA);

ST_CP_ON(); //加载数据,创造上升沿,拉高锁存器时钟

Delay(100); //延时

ST_CP_OFF(); //拉低

OE_OFF(); //打开输出 输出使能 低电平有效

}